- 17 Posts

- 86 Comments

In my first ever programming class textbook was using Allman. Probably for this reason, it is easy for a beginner to match braces. It is a lot loss common industry to my knowledge.

3·7 months ago

3·7 months agoAs you said before power on capacitor is discharged. Right after power on capacitor is still discharged, so voltage on capacitor is zero, so reset pin has Vcc. With time capacitor gets charges and voltage across capacitor increases and reset voltage becomes closer and closer to ground, until it is ground. But it is important to consider what happens at power down too. At power down capacitor is charged. If power source becomes high impedance at power down, then reset pin will probably go down to zero in time but may take a bit time depending on what source exactly does. But if power source is connected to zero at power down reset pin will observe minus vcc and slowly go up to 0. If reset pin is sensitive it may be a good idea to protect it with a diode.

3·7 months ago

3·7 months agoSimpsons predicted it once again.

19·7 months ago

19·7 months agoIf you knew about the birds and the bees, you would know that this wasn’t random.

61·7 months ago

61·7 months agoTo be fair 10^(0.000000000000000000001x) is also exponential growth. And if status quo is x=0 and removing entire management means x=10 this means even the max we can get is very little improvement. It can be “exponential” and still not so much.

254·7 months ago

254·7 months ago“Exponentially” is not synonymous to “a lot”. Exponent is a mathematical term and exponential growth requires at least two variables exponentially related to each other. For this to be possibly exponential growth a) progress should be quantifiable (removing management and treating workers well should be quantized somehow) b) performance should be quantifiable and measured at a bunch of progress points (if you have only two measurements it can as well be linear) c) performance should be or can be modeled as a an exponential function of progress in removing management and treating workers well.

I wish we had an active aoe2 community.

26·7 months ago

26·7 months agoI don’t think this will work well and others already explained why, but thanks for using this community to pitch your idea. We should have more of these discussions here rather than CEO news and tech gossip.

4·8 months ago

4·8 months agoWe should stop calling these titles confusing and call them what they are, plain wrong. This is the title of the original article. People who cannot write grammatically correct titles are writing entire articles.

3·8 months ago

3·8 months agoGrammatically speaking, doesn’t it really say that Sunak warned others? I am confused.

3·8 months ago

3·8 months agoDepending on the power consumption, you may consider not using thermal relief while connecting thermal vias for the chip (component 57) to ground layers. But this may make soldering harder so do it only if needed. Thermal vias are so close that they form 3 long dents in 3v3 plane. It is good practice to put vias a little far apart so that planes can go through between vias. This can be important since sometimes lowest impedance can be obtained when current is flowing between those vias. If you don’t need to fit 15 vias there, you may consider reducing the number and separating them a bit. You can also check the design rules for minimum copper width and minimum via clearance for your manufacturer and enter them in your CAD tool.

141·8 months ago

141·8 months agoI don’t realistically expect such ban to happen. I started banning everyone who posts about Musk instead, my feed got a lot cleaner.

6·8 months ago

6·8 months agoThird siblings who were born right after cameras got affordable have the most pictures.

Not every programmer has a github account.

3·8 months ago

3·8 months ago“City-size” at least they didn’t measure in football fields.

14·8 months ago

14·8 months agoWeb design is not the only option for someone who likes programming. Since you are still a student, there are so many options in front of you. You can be an embedded engineer and work closer to hardware, design firmware, electronic chips themselves or their verification environment. You can be a software engineer and work on business-to-business software which does not include adds and is very useful (e.g. CAD tools, inventory trackers for supermarkets and hospitals etc.). There is so much you can do, pursue something you are enthusiastic about.

But have you tried restarting your computer and reinstalling all drivers?

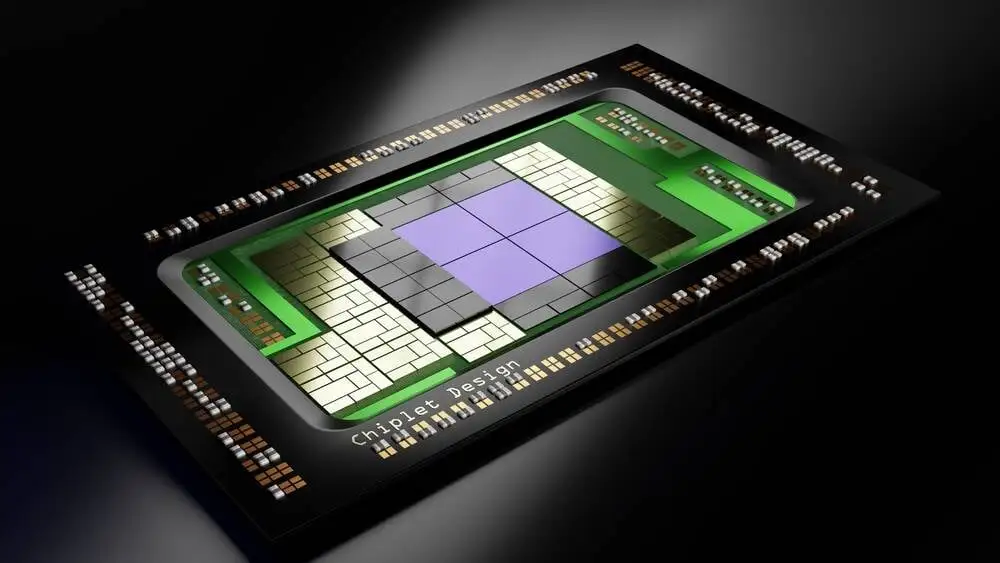

One-time programmable (memory)